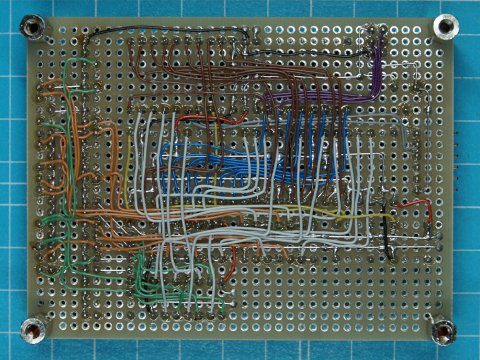

FDCボード (テスト編 その3)

カテゴリー:

ちょっと間があいてしまいました。

前回CRCエラーが出ているとはいえ一応セクタが読めるようになりました。データ転送のオーバランも発生していません。

FDCの回路を作るのは今回が初めてですが、8ビット時代に製作記事はよく読んでいました。そこではデータ転送が間に合うかどうかが大きな課題として扱われることが多く、ソフトウェアでステータスを見ながらでは取りこぼすということでいろいろな工夫がありました。

- 他の割り込みを禁止する

- DMA(Direct Memory Access)を利用する。これは速度の余裕ができてからもほかの理由で使われ続けました。

- ステータスをチェックしないでデータ転送する。そのままでは正常に転送できないので、ハードウェアでFDCへのアクセスを引き伸ばす。

それで当初は心配していたのですが、さすがに当時とはCPUの速度が一桁以上上がっているので余裕がありますね。