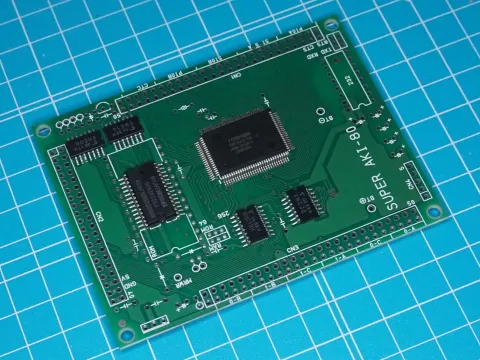

V60ボード(ソフトウェア編 その1)

前回書いたようにモニタ移植して例外処理を調べていたのですが、先日遂にコロナに罹ってしまいあまり進捗していません。

そこで現時点でのまとめを書いておこうと思います。

Universal Monitorの移植は基本MC68000用をベースにL(oad), P(unch)コマンドについてはH8/300H用を元にしています。この辺りの事情はNS32016のときと一緒です。早くMC68000用も長いアドレス対応しなくては。

いつものように移植にあたって気付いたV60の特徴を挙げてみます。