現在EMILY BoardでCDP1802 / CDP1806を動かすCPUボードを製作中ですが、動くまでまだ時間がかかりそうなのでシリアルクロックの話を少し書いてみようかなと思います。

PCと自作のマイコンを接続する最も簡単な方法の一つが調歩同期シリアルです。

マイコンボードを新たに作る場合、最終的には必要なくてもデバッグ用などにあると重宝するので、まずこれを動かすことが初期の目標になることも多いですね。

でマイコン内蔵にしろ外付けにしろUARTを動かすには(通常通信レート×16の)クロックが必要になります。

専用に発振器を用意してしまうのが簡単で自由度も高いですが、CPUクロックと共通の発振器から供給できれば部品を減らせます。その場合必要とするシリアルクロックの整数倍の発振器が使えればピッタリのクロックが得られますが常にそうできるわけではありません。PLL等を使わない限り整数分の一のクロックしか得られませんから近似値で代用することになります。この誤差はどの程度まで許容できるのか考えてみましょう。

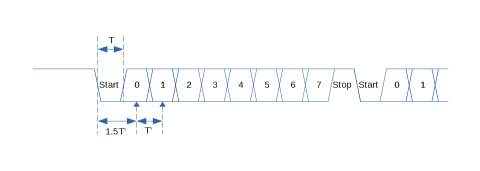

調歩同期シリアルのタイミング(8ビット・パリティ無し・1ストップビット)を示します。

T, T' は1ビットの時間で、例えば9600bpsの場合は1/9600[s]です。

送信側はT間隔でスタートビット・ビット0・ビット1・・・ビット7・ストップビットの順に送出します。

受信側ではまず立下りを検出し、1.5T'後にビット0、2.5T'後にビット1と順に取り込みます。9.5T'後にもし"L"であればフレーミングエラーとなります。0.5を足しているのはビット中央の最も安定したところを読むためです。

もしTとT'が異なっていたらどうなるでしょう?

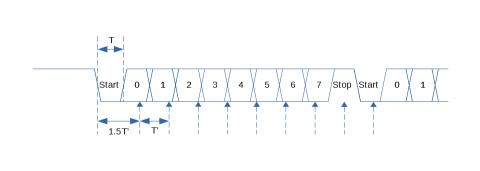

ちょっと極端ですが T' = 1.125T(15%遅い)の場合を示します。

あとのビットになるほど取り込みタイミングがビット中央から少しずつずれていくことになります。この例ではビット2がギリギリで、ビット3は境界上になってしまっています。

フレーミングエラーを起こさない限界はストップビットを読む9.5T'が9Tから10Tの間でなくてはなりません。つまり9.5(T-T')が±0.5を超えると隣のビットを読んでしまいます。

理論的には約5%が限界ということになりますね。

実際には波形がなまったりするのでビットの端を読むのは避けるべきです。特に高ビットレートの場合や伝送距離が長い場合などは要注意です。

また通信相手には正確なクロックを要求しておきながら自分はマージンを目一杯利用するというのはフェアではないですね。

個人的には相手が決まっている(こちらがマージンを食いつぶしても問題ない)場合で2%、そうでない場合は1%くらいが限度かなと思っています。

よく使われる「13分周」で2[MHz]から9600bpsを作る場合 2,000,000 / 13 / 16 ≒ 9,615 となって誤差は約0.16%となり、十分余裕があることがわかります。

専用のハードウェアを用いずソフトウェアによってUART相当の機能を実装する場合にも、タイミングにどこまでの精度が必要になるかの参考になると思います。

Add new comment