最近では見かけることのない変わったパッケージを紹介しましょう。

これはNECのμPD7800G、NEC独自の8ビットのワンチップマイコンです。仲間がカシオのパソコンFP-1000/1100のサブCPUとして使われていた以外、あまり一般には知られていないデバイスです。

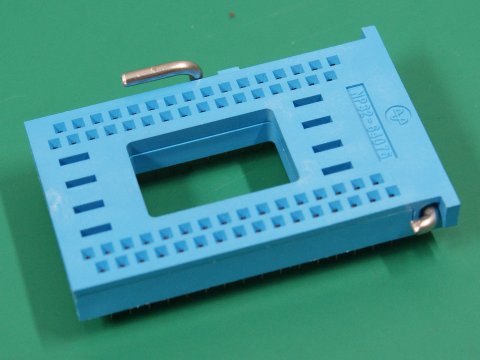

このパッケージはQIPまたはQUIP (Quad in-line Package)と呼ばれていたものです。

基板に挿すタイプのICはアナログやパワーICに使われるSIP (Single in-line Package)、SIPの足を交互に曲げたもので主にDRAMに使われたZIP (Zig-Zag in-line Package)、もっとも一般的なDIP (Dual in-line Package)、CPUなど多ピンのICに使われる底面に格子状にピンが並ぶPGA (Pin Grid Array)、そしてDIPの足を交互にしたこのQIPがありますが、ZIPとQIPはほぼ絶滅してしまいました。

どちらもパッケージを小さくするためにピン間隔を狭くしたいのだけれど、基板のパターン設計が難しくならないよう配慮したといったところでしょうか。

1.27mmでもパターンは引けますが、ピン間に配線が通せなくなります。2.54mmならピン間3本は可能(手作りは無理でも量産は可能)ですから。表面実装なら反対面は自由に使えるのでこの手の心配は無用になります。挿し部品が嫌われる理由の一つです。

これは専用のICソケット、ZIF (Zero Insertion Force)タイプのものしか見たことはありません。やはり足のモールド部分から折り曲げ部分までの距離が長いため、通常のソケットだとピンが変形してしまい正常に挿しづらいということでしょう。

ピンの位置は全て1.27mmの格子に乗るので、秋月電子で売られている1.27mmの万能基板を使えそうです。そういう観点ではシュリンクDIPよりありがたいんですがねぇ。

ピン配列は点対称ではないので、向きには注意が必要です。正しく配線されていれば挿す時に間違える心配が無いのはメリットかもしれません。

Add new comment