ずっと探していたMC68kボードの資料をやっと発見しました。これを書いたのは高校生の頃のはずなのでちょっと懐かしいですね。

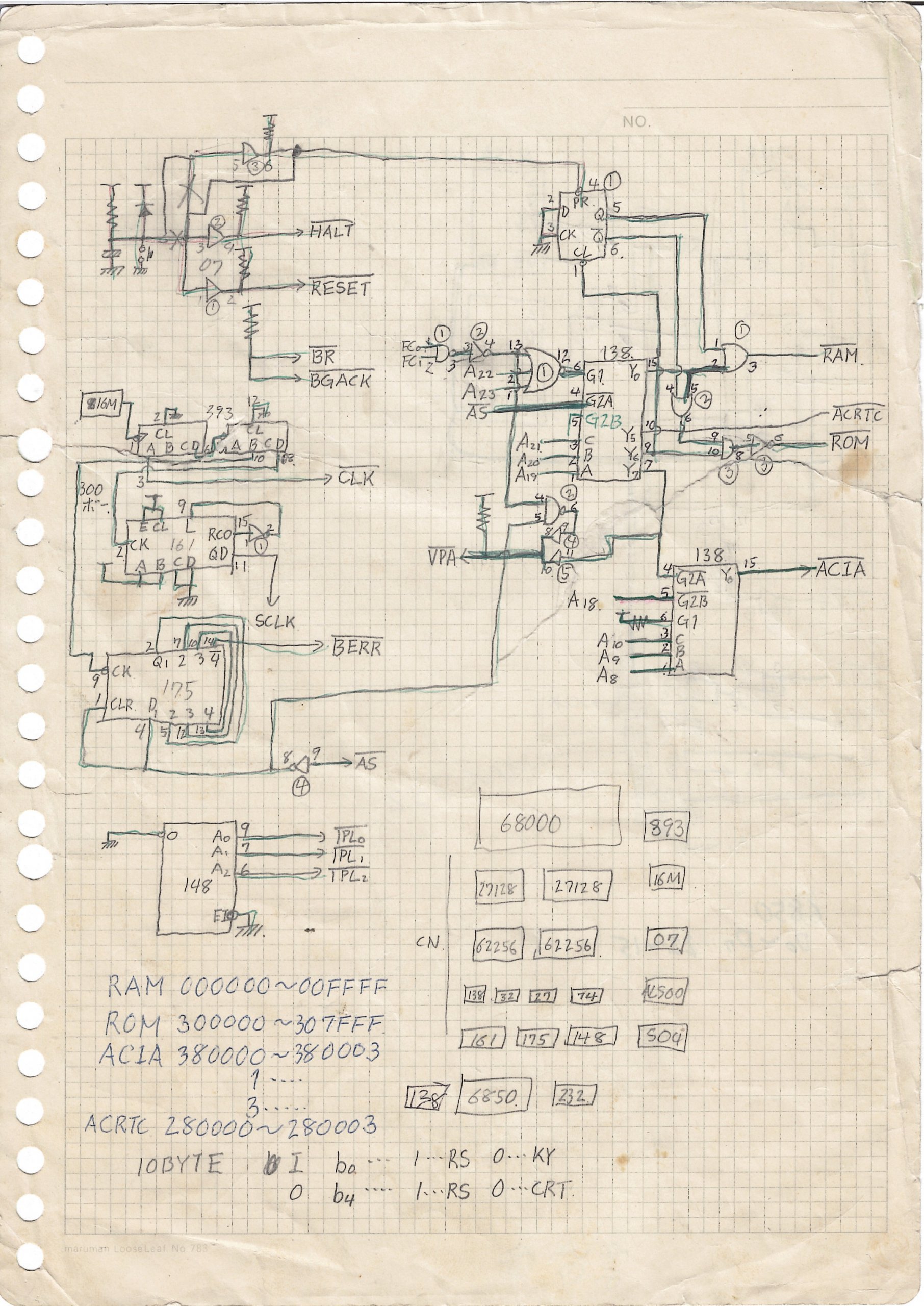

1枚目はリセット・クロック・バスエラー検知・割り込みとアドレスデコーダの回路図です。

これは第1期工事時点のものです。ゲート等に書かれている丸付き数字は同一パッケージに入っているユニットの番号、赤や緑は配線したときのチェックですね。

左上のリセット回路の不適切なことは以前書きました。この図では修正が入っていますが、現物を修正したのかは不明です。

その下はクロック回路、16MHzを分周して8MHz, 250kHz, 62.5kHzを作り、8MHzはMPUクロックに、250kHzはさらに下の161で13分周してシリアルのクロックにしています。

下の175はリセット付きのシフトレジスタを構成していて、62.5kHzのクロック4つの間ASがアサートされているとBERRをアサートしてバスエラーを発生させます。ASがアサートされたままというのはVPA, DTACKを誰もアサートしなかった(=想定外のアクセス)ということで放っておくとMPUが止まったままになるのでエラーにするわけです。

148は割り込みのエンコーダですが、この時点ではまだ使っていないようですねシリアルポート用に使っています。

右上のフリップフロップはリセット時にROMとRAMを入れ替えるためのものです。MC68000はリセット時にメモリの0~7番地を読んでPC, SSPを初期化するのでこのアドレスにはROMが必要です。しかし8~1023番地には割り込みベクタがあるので書き換えられないと困ります。

これにはいくつかの方法があります。

- アドレス0~7をデコードして、ここだけはROMを見せる。

- リセット直後はアドレス0付近にROMを見せておき、起動したらRAMに切り替える。

このボードではリセット時に0番地からのRAM領域にROMを見せておき、本来のROMアドレスへのアクセスが発生したときに本来のRAMに戻すようにしてあります。PCの初期値にはROM内のアドレスが入るので、PC, SSPの初期値を読んだ直後に最初の命令をROMから読もうとした時に戻るわけです。

せっかくのDフリップフロップのD, CKを殺してR-Sフリップフロップとして使っていますね。

下はアドレスデコーダ、MC68000のアドレスは多いのでフルデコードはしていません。

FC0, FC1のANDをとっているのは割り込み応答サイクルの検出です。本来はFC2も入れなくてはいけないのですが、含めなくても平気です。MC68020以降ではアドレスも加味しないとコプロセッサアクセス等と区別できないのですが、これもMC68010までなら不要です。

割り込み応答サイクルではVPAをアサートして自動ベクタにします。

ここにはACRTCなどという信号名も書かれていてHD63484の接続を考えていたことがわかりますね。

下の方にはアドレスの表と基板上の部品配置も書かれています。

ここには2つある138が実基板では1つしかないのは、第2期工事でMC68881の場所を作るために外したのかもしれません。

一番下の「IOBYTE」は後にCP/M-68kを移植したときのメモと思います。

Add new comment