カテゴリー

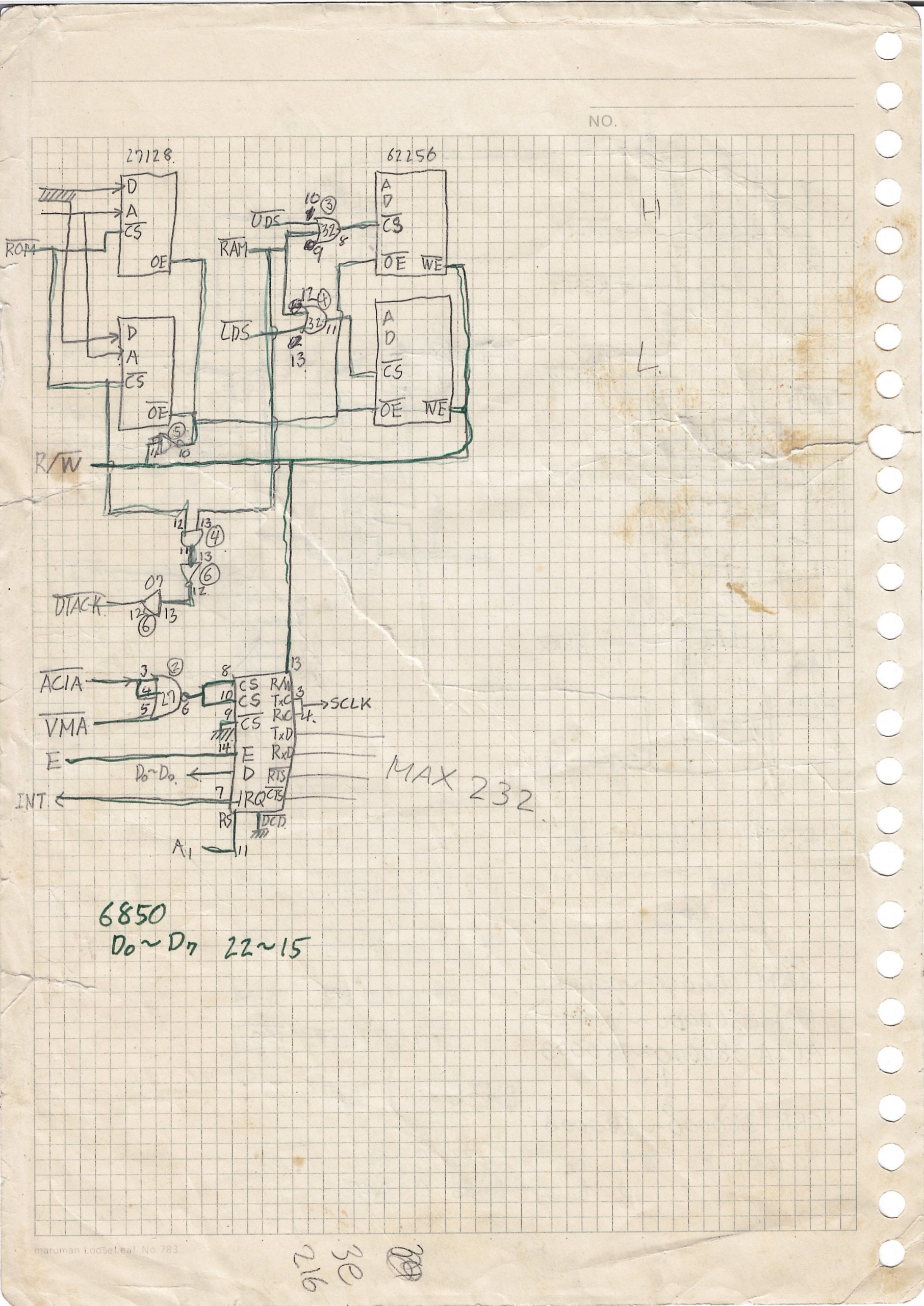

2枚目(裏面)はメモリとACIAです。

上はメモリです。

単純に接続するだけのバス配線は省略されていますが、アドレスバスはMPUのA1をROM・RAMのA0へというように1つずらして接続、データバスはMPUのD8~D15を上位側メモリのD0~D7へ、MPUのD0~D7は下位側メモリのD0~D7へと接続します。

ROMは常にワードアクセスです。バイトアクセス時にも16ビットデータを読み出し、不要なバイトデータはMPUが無視します。

RAMはバイト単位の書き込みができないと困るのでCSの論理にUDS, LDSを加えて切り替えています。

本ボードではCSを切り替えていますが、読み出しはROM同様にワードで構わないので、WEを上下に分ける手もあります。

DTACKはROMかRAMのアクセスがあったときに返すようにしています。アドレスとASの確定ですぐに返しているのでウェイト無しです。

ROMの条件にR/WがHであることを加えれば、ROMへの書き込みをバスエラーとして検知できるようにもできます。

下はACIA (シリアルポート)です。昨日割り込みは使っていないと書きましたが、ACIAで使っていました。MAX232を使ったレベルコンバータ部は定型回路なので省略されています。

この資料は最初に書いたものなのでMC68881やボーレートの切り替えは含まれていません。

MC68881はメーカ資料にMC68000の16ビットバスに接続する例が載っていましたのでそのまま利用したはずです。

ボーレートのところは昨日の回路で393から161へクロックを取り出すところを切り替えているだけです。間違えて2つをONした時に393の出力を短絡しないようにシリーズにRを入れて保護しています。

Add new comment