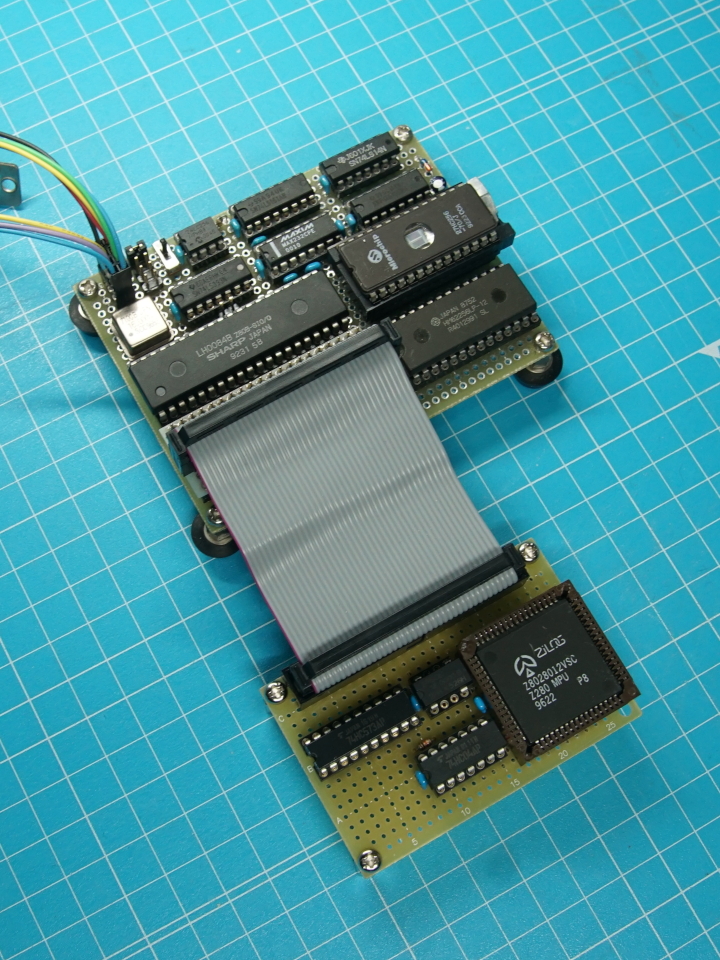

以前入手したZ280ですが、持っているだけではなんなのでボードを作ってみました。

これがZ280ボード、メモリ回路とか結構面倒なのでまずは動作確認ということで既存ボードのZ80 CPUを置き換える形で製作しました。

Z280にはZ80と同じ8ビットバスのモードと、Z8001と同様の16ビットバスのモードがあります。ここでは前者を使うことで比較的容易にZ80の代わりに使用することが出来ます。

まずデータバスとアドレスバスがマルチプレクスされていますので、74HC573でアドレスをラッチして分離します。74HC04はラッチ信号ASの反転用です。

大きな問題はCLKです。Z80 CPUではもちろん入力信号ですが、Z280では内部クロックを分周して作られる出力信号なのでそのまま接続することは出来ません。

- 一番簡単なのはZ80ボード側でCLKの供給を止める方法です。市販のパソコン等のアクセラレータとしては使いにくい方法です。

- Z80ボードから供給されるクロックとZ280の出力するクロックが一致するようにPLLを組むという手もあります。

- Z80ボードのクロックとは非同期でZ280を動作させる方法もあります。かなりの回路規模になると思われますが、Z280ボード側にローカルの高速メモリを積むなど自由度の高い設計も可能になります。

Z80ボード側で他にCLKを使用していないか使用していてもバスサイクルとの同期が不要なら接続しないという選択肢もあります。

今回は自作のボードで改造が容易だったので最初の方法を採用しました。「MAA-1を小改造」はこのためのものです。

他は基本直結できそうです。WAITはサンプルされるタイミングが変わっていますが、MAA-1では使用していないので特に何もしていません。

MAA-1のZ80 CPUを抜いてこのように接続します。

CLKとRFSHが出ていることは確認できました。Z180をZ280にリマークしたものが存在するという情報があったのですが、どうやらその心配はなさそうです。

これでプログラムも走ってくれれば良かったのですが、残念ながらだめでした。

Z280はデフォルトで命令キャッシュが有効になっているようでリセット直後にメモリアクセスをした後はよくわからないメモリライトを繰り返しています。アドレスとデータがマルチプレクスされているうえにリフレッシュアドレスも出力されているので周波数カウンタごときではバスを見てもよくわからないのです。

というわけでバス観測用の治具基板を製作中です。

Add new comment