PLLシンセサイザの続きです。

間があいてしまったので今困っていることをまとめてみます。

- 基準周波数を下げると不安定になる

100kHzではいいが一般的な10kHzにすると安定しない - 出力周波数を下げると不安定になる

1MHz付近まで下げると安定しない - ロック検出をどうするか

1.と2.はループフィルタ問題だと思われるので本を読み漁っているのですが......

学生時代は制御研究室にいたこともあってフィードバック制御は馴染みではあるのですが、PLL回路には位相比較器とかVCOなどの見慣れないものが含まれています。本を頼りに求めてみたのですがどうも桁が違っているようで、何かを勘違いしているのかもしれません。

じっくり本は読み直すことにして、勝手のわかるフィルタ部分だけ先に求めてみます。

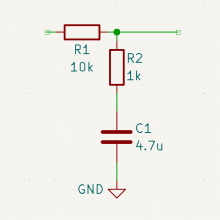

実験に使っているのは以下のラグ・リード・フィルタです。

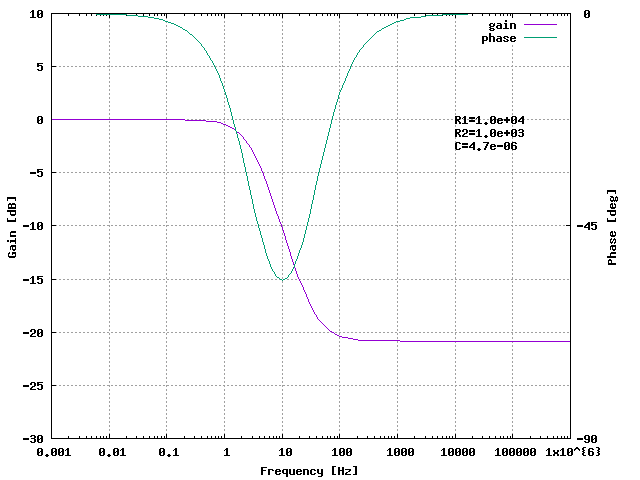

R1=10kΩ, R2=1kΩ, C=4.7μF についてボード線図を書いてみます。

全域にわたって位相遅れが最大でも60°程度に収まっています。これってループゲインにかかわらず発振の心配はいらないということなのかな?

そうすると問題になっている不安定さはループフィルタの問題ではないのかもしれません。

他に気になっているのはVCOのF-V特性がリニアではないというところ。F-I特性の方が良さそうなのですが、今はFET一つで済んでいるリングオシレータの電源がちょっと面倒なことになりそうです。

R2と並列にCを入れて高域を減衰させている例も多いので、それも試してみようと思っています。ただその場合は高域でどんどん遅れていくはずなのでゲインもちゃんと検討しなくてはなりません。

3.のロック検出については困っているというよりも未着手に近いといった状況です。

MC145157のLD(Lock Detect)ピンは単にロックすると"H"になるようなものではなく、矩形波の"L"の期間がロックすると短くなるというものです。位相比較器への2つの入力のEx-NORが出ている感じかな。デューティで度合いがわかる(=閾値を自由に設定できる)点が便利ですね。

ワンショットなどで処理している例が多いですが、せっかくAVRマイコンがいるのでうまい表示ができないか考えているところです。デューティ測ってバーLEDが簡単かな。

今回は途中経過だけになってしまいました。早く何らかの進展を書きたいですね。

Add new comment