もう「その10」と2桁に達してしまいましたが、当面は何か進捗があるたびに書いていこうと思います。

今回は何が進捗したかというと、出力周波数を下げていくとロックしたりしなかったり不安定になる問題です。

1MHzというのはVCOを単独で動かして求めた可変範囲をもとに出せるはずと思っていたわけですが、ループフィルタの出力の範囲が狭い、あるいはその付近でVCOのF-V特性が急峻になっていて周波数が安定しない、という可能性もあります。

前回リングオシレータの電源云々と書いたのは後者の対策だったのですが、ちょっと実験するだけならもっと簡単な方法がありました。

それはリングオシレータを1段から5段に変更してみることです。これで同じ入力電圧に対する周波数は約1/5(容量などの影響でもうちょっと下がるはず)になります。

試してみると設定下限の300kHzまで安定に動作します。代わりに上限も下がって14MHz程度までしか出せなくなりました。

これで下は300kHzから上は50MHz程度まで出すことができ、当初予定の1~25MHzはカバーできました。段数の切り替えをしなくてはいけないのがちょっとアレですが、300kHzから50MHzまでスイープするような使い方はしませんからあまり困りません。ジャンパの差し替えは面倒なのでアナログスイッチか何かで切り替えたいとは思います。

もう一つ進展というか......

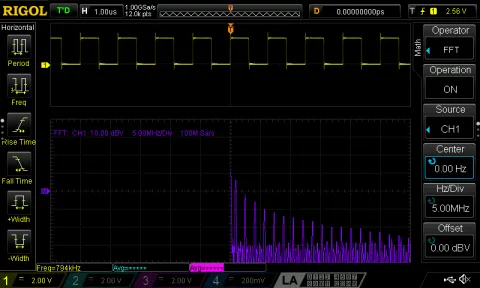

PLLの動作見るのにスペアナ欲しいな、だけどこれ以外何に使うんだ、などと考えていたのですが、実は持っているオシロMSO1074ZはFFTアナライザの機能も持っていたのでした。

ということでちょっと試してみました。

矩形波なので800kHzの他、2.4MHz, 4MHz, ... と奇数次高調波が出ていますね。

これで何が起きているのかもうちょっと調べられるのではないかと期待しています。

Add new comment