カテゴリー

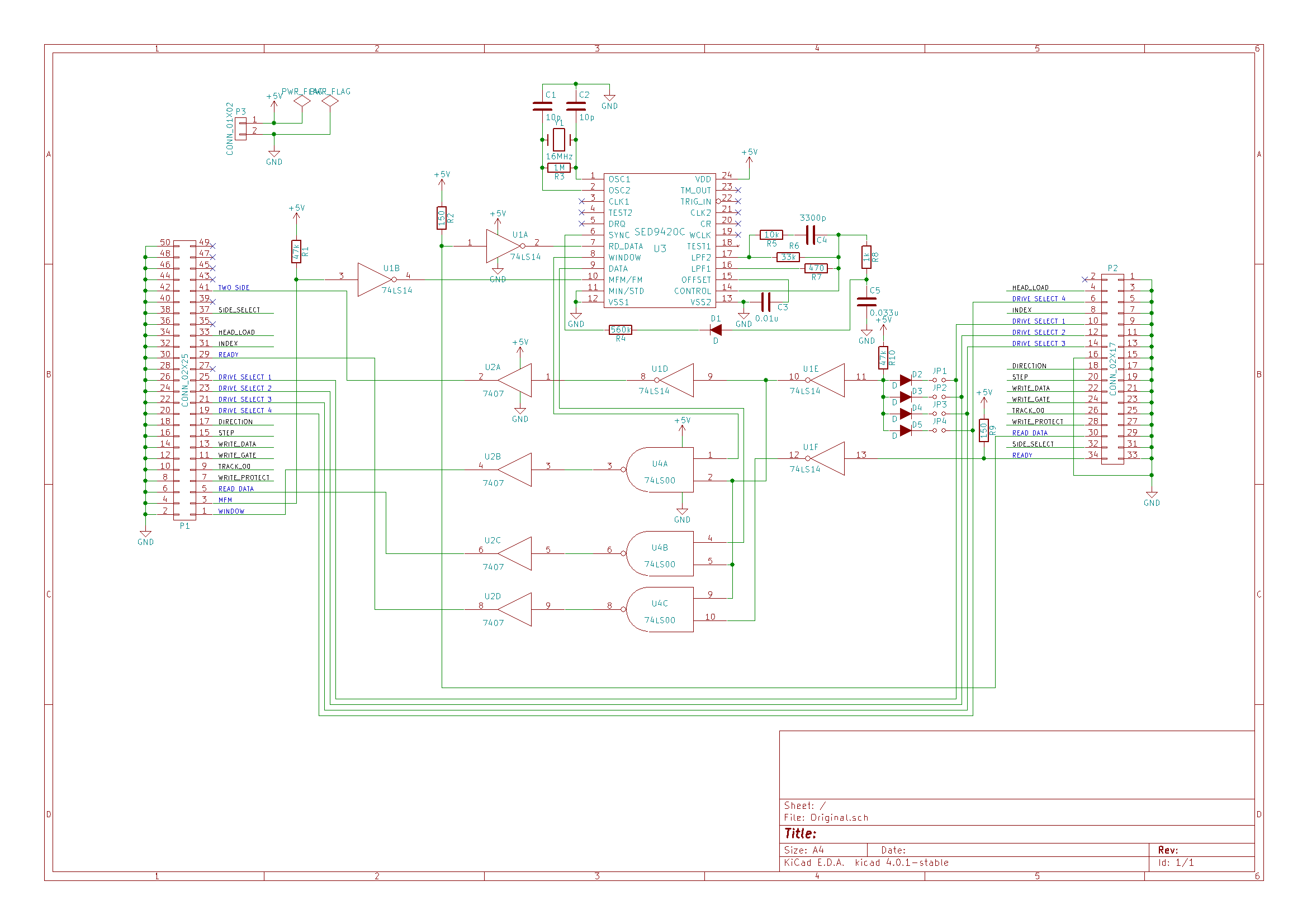

先日のデータセパレータの回路図、ドライブ構成を変更できるように修正してみました。

NECのPC-8001, PC-8801, PC-9801シリーズの8インチFDDインターフェイスに3.5インチ・5.25インチのFDDを接続するためのものです。

元は私が25年以上前になにかの雑誌記事を参考に製作したものです。その現物から回路図を起こし、修正を加えました。現在動作確認する環境がありませんので、この回路は動作未確認であることをご承知置きください。

また元々は学生時代に「とりあえず動作すればよい」との前提で製作したものですので、本来必要なものが省略されていたりもします。

もし製作される場合は各自の責任でお願いします。

以下、注意点などをあげますので、参考にしてください。

- 50ピンバス(8インチ)側にはターミネータがありません。末端にターミネータのついたドライブを接続するか、この基板が末端になる場合はターミネータの追加が必要になります。

- 一部の信号は本基板から8インチの末端側と34ピン(3.5インチ・5.25インチ)側に分岐する形になります。ターミネータも並列に複数が接続される状態になります。通常34ピン側のターミネータは抵抗値が大きく問題になることは少ないと思いますが、気になる方は一度74LS14で受けてから7438などでドライブすると良いと思います。中継しない場合は分岐側の配線は短くすることをお勧めします。

- JP1~JP4は34ピン側に接続するドライブに合わせてショートしてください。例えばドライブ1,2は8インチでドライブ3,4に3.5インチを使用する場合は、JP3とJP4をショートします。

- 見ればわかると思いますが、コネクタP1, P2から短い線だけが描いてあるものは、同じラベルのもの同士を接続します。

- FDD回路のオープンコレクタのドライバは通常7438を使用します。この回路で74LS00+7407になっているのは当時手持ちを使用しただけで特に意味はありません。

- SED9420CのDRQ, SYNCはμPD765の同名の端子に接続するもののようですが、DRQは50ピンの信号に含まれていません。50ピンコネクタはNEC製の8インチFDD FD1165Aそのものですが、このFD1165Aの内蔵データセパレータもSED9420Cなので無くても問題ないはずです。SYNCの方は27ピンにVFO SYNCとしてありますので、本来はこれを74LS14かなにかで受けて接続すべきなのかもしれません。

- R4とD1の回路をどこに接続すべきか、実は自作のデータセパレータ基板 (回路図編)の時から謎でした。資料によってCONTROLとするものとR8-C5間とするものがあったのです。気になって「SED9420C/21Cとその使い方」(著者は諏訪精工舎の方)を調べたのですが、今度は左側がSYNCではなくDRQになっているではないですか(右側はR8-C5間)。

結局よくわからないので現物のままにしてあります。一応これで動いていたわけですし。

参考文献・関連図書

川崎健(1983)「SED9420C/21Cとその使い方」,『電子科学』1983年10月号, pp.81-86, 産報

コメントを追加