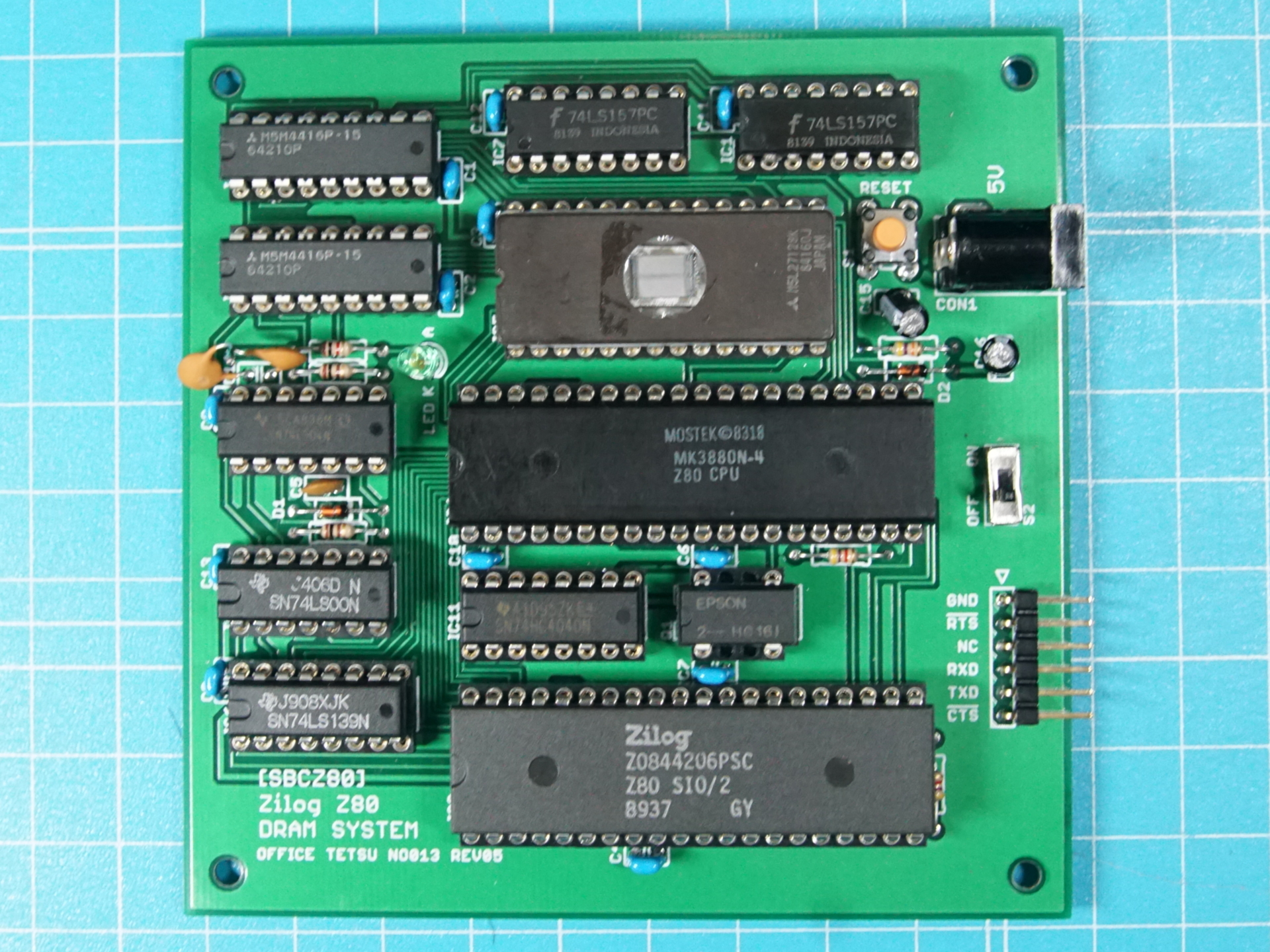

書泉ブックマートで『ザイログZ80伝説』を買ったらCD-ROM・プリント基板付きの限定版が手に入りました。Z80のボードは既に何枚も作っていますが、せっかくなので組み立ててみます。

これまでのSBCシリーズは8cm×10cmでしたが、これは10cm×10cmで密度も最大クラスでしょう。

面積をくっているのはRAMです。SRAMなら24~32ピンのDIP1つで済みますが、18ピンのDRAMが2つに制御用のロジックが4つ必要となっています。今となってはこの容量ならSRAM積んだ方が有利ですが、このボードはDRAMを動かしてみたいということで設計されたとのこと。

それではいつものように基板上のデバイスを見ていきましょう。

中央の MK3880N-4 Z80 CPU というのがもちろんご本尊のCPUです。数日前にTwitterに上げた写真と変わっているのは次のような理由です。

- 当初CERDIP品を載せたが動作せず

- ちょうど手元にあったMAA-1ボードから借用して動作

- ソフトウェア編で記述予定の電源ON直後の問題切り分けにMAA-1を動かす必要があり戻す

- 両ボードを交互に動かせないと不便なのでこのMOSTEK製を探し出して搭載

このボードは現在クロック2.45MHzで動作させていますが倍にすることも可能なので6MHz品に交換するかもしれません。

ここから時計回りに見ていくことにします。

SG-8002DCとSN74HC4040Nはクロック、9.8304MHzを1/4に分周して供給しています。Z80 CPUのクロック入力はTTLでドライブする場合はプルアップ抵抗が必要になりますが、CMOSの74HCならそのままでOKです。さらに分周してシリアルのクロックを得ます。

Z0844206PSC Z80 SIO/2はシリアルの石ですね。調歩同期に使うには勿体無いくらいですが、これもZ80ファミリのモード2割り込みを使ってみたいという意図で選択されたようです。

あと今回は指定通りSIO/2を使っていますが、ボンディングオプションにより異なっているピン25~29は未使用なのでSIO/0やSIO/1でも問題なく使えると思います。

SN74LS139Nはアドレスデコーダです。64kBのメモリ空間を16kBずつに4分割して0000H~3FFFHをROMに、8000H~0BFFFHをDRAMに割り当てます。

SN74LS00NとSN74LS04NはDRAMの制御信号を作ります。タイミングはCR積分回路による遅延を使い、220pFのキャパシタは手持ちが見当たらなかったので470pFを2つ直列にして代用しています。

M5M4416P-15は16k×4bitのDRAMで、2つで16kBのメモリを構成します。実はこれだけが新規に調達したパーツです。TIのTMS4416は手持ちがあったのですが、これはリフレッシュの条件が違っていて使用できません。

74LS157PCはアドレスのマルチプレクサです。1981年製と古いものですが、昔スティックで購入して死蔵していたものです。

専用基板を使用していますので(古いCPUが死んでいたらしいことを除き)ハードウェアには特に問題はありませんでした。次回はソフトウェア(Universal Monitorの移植)についてを予定しています。

Add new comment