PLLシンセサイザ(その4)

また間があいてしまいましたが、PLLの実験再開しました。

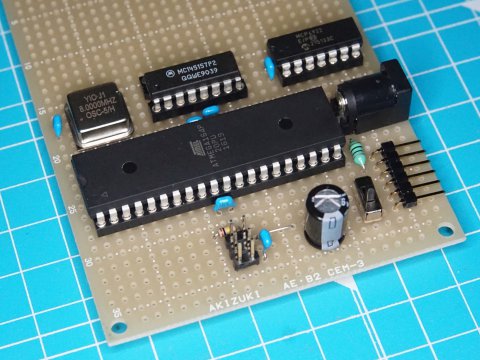

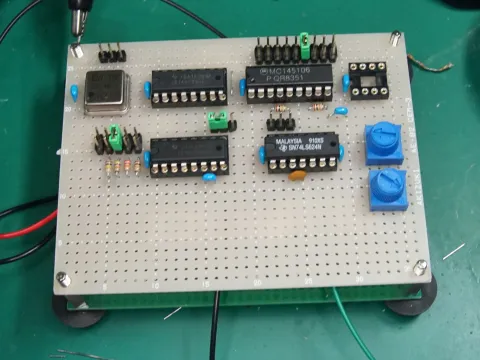

とはいえこれまで動かしていたボードは、(1) Nの設定変更がかなり面倒くさい、(2) VCOとしてリングオシレータも試してみたいが基板の空き面積がギリギリ、といった問題があります。そこで新たに別な実験基板を作ってみました。

秋月のBタイプ基板を縦に使っています。

上部の空きエリアにはループフィルタとVCOをサブ基板で載せ替えられるようにする予定です。これでVCOをいろいろ試せるようになるはずです。

一方Nの変更はシリアルポート経由でターミナルから変更できるようになります。