PLLシンセサイザ(その14)

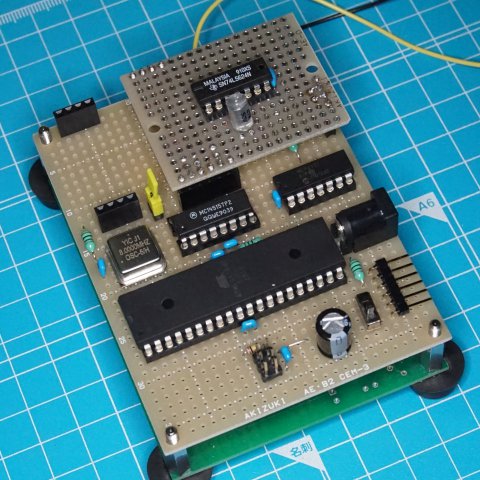

今回はその9で軽く触れたリングオシレータの電源を電流制御にするのを試したいと思っていたのですが、いろいろあって全く進捗していないので......

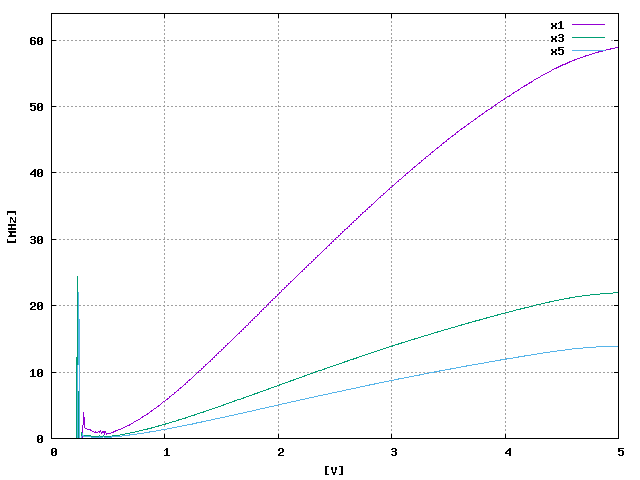

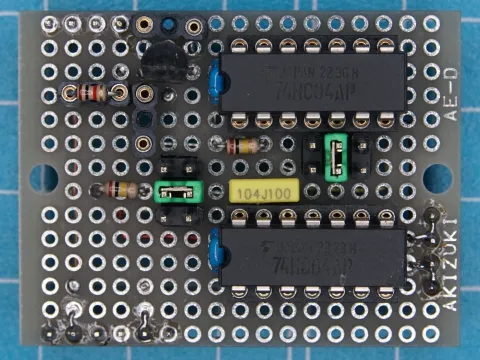

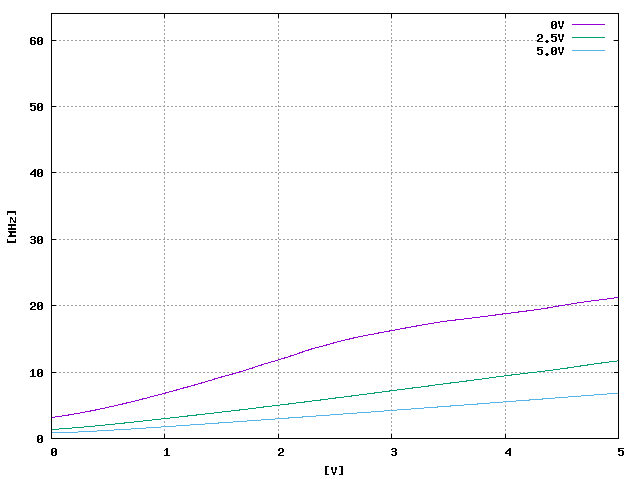

初期に作った74LS624にるVCOと74HC4046によるVCOのF-V特性を測ってみました。

まずは74LS624です。

Cx=47pF でRNGを 0V, 2.5V, 5V と変化させた場合です。

リングオシレータを見た後では可変範囲狭いなという印象が強いですね。

ただ下から上まで単調で直線性も悪くないので、何か変な現象が出たときの比較用には良さそうです。

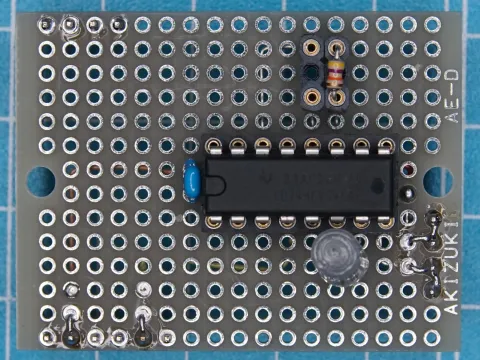

続いて74HC4046です。