データセパレータの基板がもう一枚出てきました。

前回のものと似たような構成です。

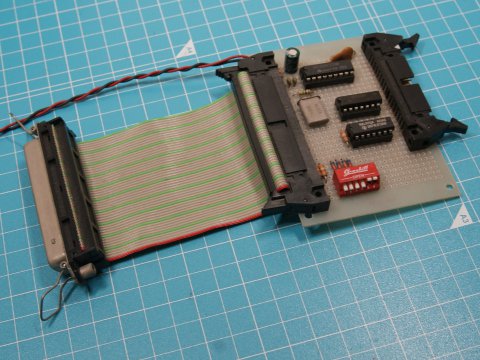

50ピン側にはDDKの57シリーズコネクタが1つのみなので末端に接続しますが、ターミネータはありません。34ピンコネクタへ直結している信号は3.5/5.25インチドライブ側で終端されることを前提にしています。使わない信号は未終端になりますので途中に8インチのドライブは接続してはいけません。おそらくはPC-286NOTE F, PC-386NOTE A用に製作したものと思います。

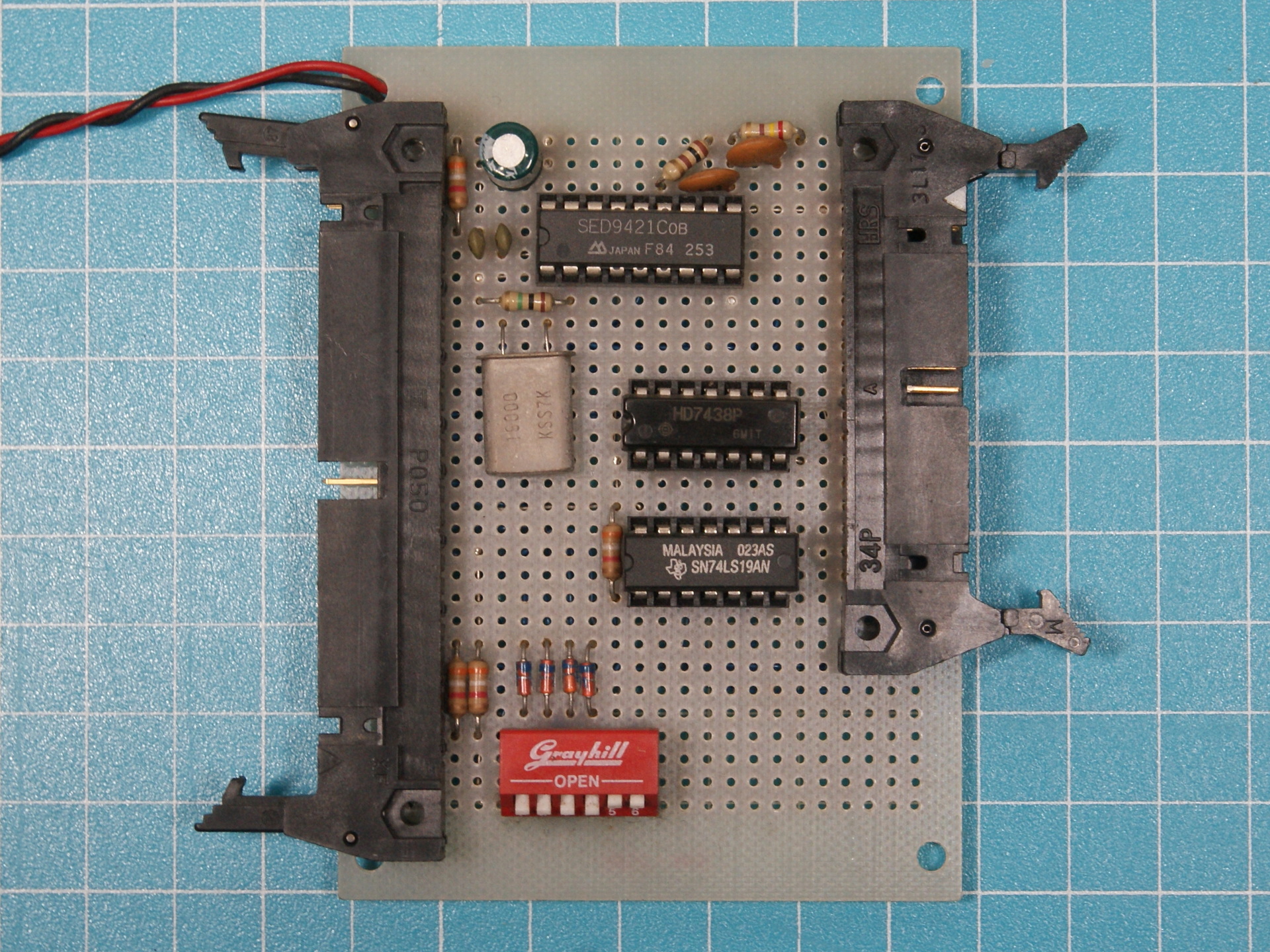

これが基板の表面です。

メインのデータセパレータICはSED9420ではなく、SED9421COBを使用しています。ピン数も24ピンから18ピンへと少なくなっていますが、これはフィルタの切替回路とタイマが省略されているためになります。

PLL方式のデータセパレータは内部のPLL回路を読み出し信号にロックさせるわけですが、SED9420ではデータエリアの前は速やかにロックさせるために応答を早くしてデータエリアではノイズ等でロックが外れるのを防ぐために応答を遅くする対応をしています。

SED9421はこの切り替えを省いてPLLの応答は常に一定になるようにします。

HD7438Pはオープンコレクタ出力のNANDゲート、FDD回路では定番のICです。

その下のSN74LS19ANはシュミットトリガのインバータ、通常は74LS14を使いますがなぜこれを選んだかは不明です。機能もピン配置も共通の改良版ということでどちらを使用しても問題ないはずで、単に手持ちを使っただけではないかと。

下のダイオードとスイッチはどのDSnでこの回路を有効にするか、選択するためのもの。回路図編-2で新たに考えたとたんにこれが出てきて、しかもやっていることはほとんど同じでした。

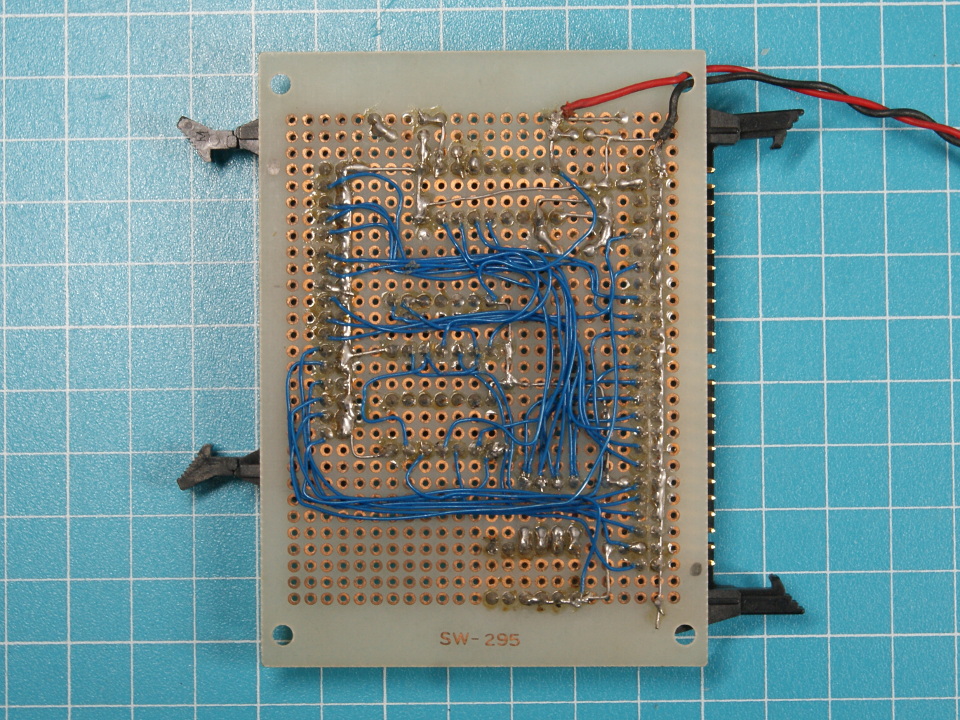

この2枚目のデータセパレータ基板を製作した記憶はまったく無かったのですが、裏面の配線を見る限りどちらも私が製作したものとしか思えません。

SED9421 pinouts?

do you have the pinouts for the SED9421COB?

Re: SED9421 pinouts?

1 OSC1

2 OSC2

3 CLK1 (Clock for uPD765)

4 NC

5 RD DATA

6 WINDOW

7 DATA

8 MFM/nFM

9 MIN/nSTD

10 Vss (GND)

11 CONTROL

12 OFFSET

13 LPF

14 WCLK

15 CLK2 (Clock for FD179x)

16 NC

17 NC

18 Vdd (+5V)

If you need more information, please let me know.

Add new comment