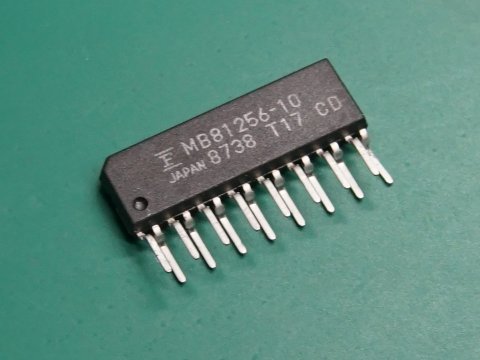

以前、LBP-A404EやMicroline 801PSで取り上げたことのあるZIPのICの未実装品を見つけました。

富士通のMB81256-10PSZ、256k×1bitのDRAMです。DRAMとSDRAMで紹介したMB81256-15と同じもので、こちらは「-10」ですからアクセスタイムが100nsの高速版ですね。

型番の「PSZ」がパッケージがZIPであることを表していますが実物へのマーキングはされていません。見ればわかるので省略したのでしょうか。

各ピンはモールドから出てくるところでは1列に並んでいますが、すぐに交互に上と下に曲がっていて1/2ずれた2列になります。列毎のピン間隔は100mil(2.54mm)ですから、根元の間隔は50mil(1.27mm)になります。そのまま1.27mmのSIPにするとプリント基板の設計に無理が生じるのがZIPにする理由でしょう。

SIPやDIPのピンは根元が太くなっていますが、これは太くする余地がほとんどありません。さらに曲げてあるので非常にデリケートで小さな力でも容易に変形してしまいます。ZIFではないソケットは使用できませんし、保管にも注意が必要です。

メリットは基板の実装密度を上げられることです。DIPだと列間は300milなので隣との間隔を100milとして400milごとに1つですが、ZIPなら列間は100milなので200milごとと倍にできます。単品種を大量に使用し、配線のほとんどが並列接続となるDRAMにピッタリなパッケージといえるでしょう。

実際DRAM以外でZIPはあまり見かけませんでした。

表面実装が一般的になるとピンが基板を貫通しているのはいろいろと制約になってきますから、PLCCやSOJに取って代わられてしまいました。とても短命だったパッケージです。

Add new comment