またちょっと面白いメモリ入手してみました。

IntelのD87C64というUVEPROMです。27C64と似たような型番ですね。

27C64は汎用のUVEPROMですが、87C64の方はマイクロプロセッサファミリの一員です。それで何が違うかというと87C64は8085, 8088, 8051といったマルチプレックスバスのプロセッサに接続しやすいようにアドレスラッチを内蔵していて、ALE/CEの立下りでA0~A7がラッチされます。

ですからA0~A7とD0~D7を並列に接続しておけばそのまま接続できるというわけです。

ならいっそAD0~AD7にしてくれればピン数も減るし、配線も少なくなるのにと思いますよね。でもそうしなかったのはROMライタへの配慮なのではないかと考えています。ALE/CEとA0~A7のタイミングに若干の制約が生じる以外27C64と同じように書き込めますから。

ちょっと不便なのはALE/CEとOEしかないことですね。たとえば8085に接続するならアドレスデコーダの出力・IO/M・ALE・RDをこの2本にまとめなければならないので結局ゲートが必要になってしまいます。

ちなみに256kbitの87C257ではALE/Vpp, CE, OEの3本になって少し改善しています。

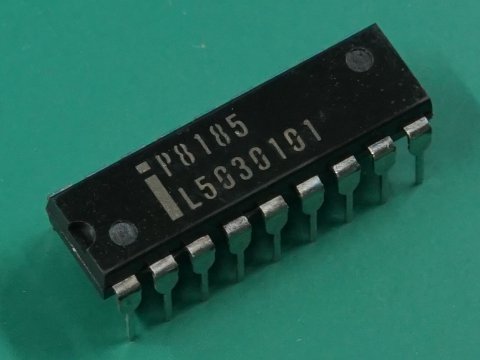

もう一つがこのP8185、1k×8bitのSRAMです。

これもアドレスラッチ内蔵のもので、こちらはAD0~AD7になっています。おかげで18ピンと小さなパッケージに収まっていますね。

CE1, CE2, CSと正負両方のセレクト信号がある上にALEも独立しているというありがたい仕様になっています。

やはりROMと異なりライタを考慮する必要がないので自由に設計できたということでしょうか。

8085 + 8755/8355 + 8156 という定番の組み合わせがありますが、I/Oは少なくてもいいからROMが欲しいときには8755/8355を87C64に替えたり、RAM容量が欲しいときには8156を8185に替えたりというのも良いかもしれません。

NSC858を加えたらラッチ無しでシステム組めますね。

NSC858を加えたらラッチ無しでシステム組めますね。

NSC800も8085もI/Oアクセス時にはA0

NSC800も8085もI/Oアクセス時にはA0-A7と同じものがA8-A15にも出力されるので、普通の8251とかでもラッチ無しでつながるはずです。

でもラッチ無くせても、アドレス・IO//Mなんかのデコーダが残ってしまうんですよね。8085+87C64+8185まではダイオードでなんとか3ICにできそうなんですが、これに8251足すとIO//M→/CEのインバータが必要に...。

Add new comment