前回は74LS624によるVCOを作成しましたが、当初の計画である1MHz~25MHzには上限が足りない上にV2のコントロールが必要です。

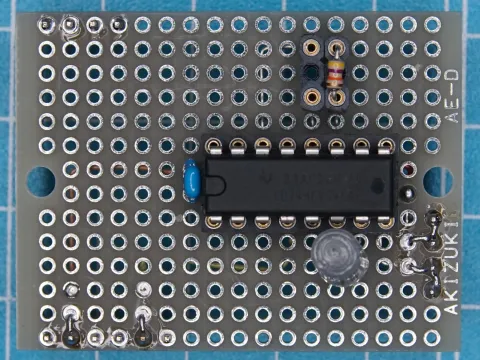

そこで74HC4046によるVCOも作ってみました。

これも部品点数の少ないシンプルなものですね。74HC4046も前に動かしているので基本それを踏襲していますが、R1を切り替え式から挿し替え式に変更しました。さらにR2も必要に応じて挿せるようにソケットを用意しました。

とりあえずR1=47kΩ, R2=∞(Open)としています。

これで前回同様に周波数の可変範囲を調べてみると、0.94MHz~23MHzとわずかに広くなったうえにV2のような別途コントロールしなくてはならないものもありません。

これで一応1MHz~20MHzはカバーできる(本当は25MHzまで欲しい)と喜べればいいのですが......

これは電圧を0~5Vまで変化したときの話で、実際にPLLとして動かす場合の電圧の範囲はもっと狭くなってしまいます。

ということで74LS624, 74HC4046の両者にフィードバックをかけて動かしてみました。基準クロックは8MHzを80分周した100kHzとしています。当初10kHzを試したのですが周波数が安定しませんでした。前のMC145106を使った基板でも10kHzだったのでジッタの原因はこれだったのでしょう。

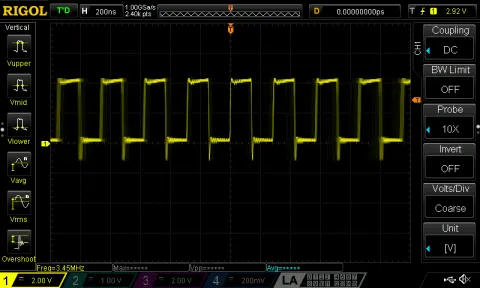

まずは74LS624から、安定に動作する周波数の下限と上限を探ってみます。

ちょっとジッタがありますね。ギリギリの周波数を攻めすぎたかな。

可変範囲は3.45MHz~18.9MHz、下はV2=0Vで固定しているためですが5Vにしてもギリギリ1MHzまで下がるかどうかといったところでしょう。上も足りていないのであとはCxを切り替えるか、アンプを入れて制御電圧を目一杯振れるようにするか、くらいでしょうか。

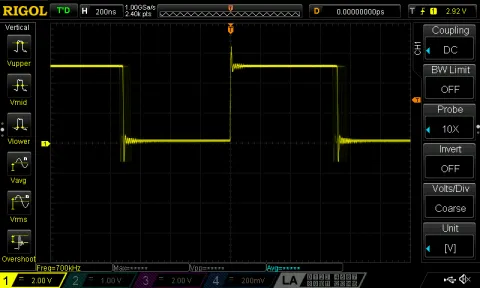

続いて74HC4046です。

こちらは700kHz~22.1MHz、バラツキ等を考慮して余裕をみても1~20MHzはカバーできそうですね。

でもこうなると欲が出てきます。次はリングオシレータを使ったVCOを試してみることにします。

私のTwitterを見ている方は気付いていると思いますがVCO単体では既に動いています。ただPLL回路に組み込むと周波数の下の方が安定しないのです......

コメントを追加