TMS9900NL

TMS9902と一緒に入手したものです。

Texas InstrumentsのTMS9900NL、以前取り上げたTMS9900JDLのプラスチックパッケージ版です。

デートコードらしき数字が「8323」と「9035」と2通り記載されていますがどちらでしょう?

フィリピン製です。

キズが多くて中古っぽいですが、妙に綺麗なものよりリマーク品の可能性低そうでかえって安心かもしれません。

TMS9902と一緒に入手したものです。

Texas InstrumentsのTMS9900NL、以前取り上げたTMS9900JDLのプラスチックパッケージ版です。

デートコードらしき数字が「8323」と「9035」と2通り記載されていますがどちらでしょう?

フィリピン製です。

キズが多くて中古っぽいですが、妙に綺麗なものよりリマーク品の可能性低そうでかえって安心かもしれません。

EMILY Boardの12/16ビットワード対応を始めたのですが、意外に大規模な変更になってしまってだいぶ時間がかかりそうです。

ということで今回は最近入手したデバイスを取り上げようと思います。

Texas InstrumentsのTMS9902ANL、ACC(Asynchronous Communication Controller)と呼ばれるものです。いわゆるUARTですね。

この手のデバイスで18ピンというのは少ないですが、これはパラレルバスではなくCRU(Communication Register Unit)というシリアル通信でCPUと接続するためです。それでも10本ほどの線が必要ですが...

CPUとの接続がこのように特殊なためTMS9900ファミリ以外には使いにくいと思います。

予告どおりソフトウェア編です。これまでの「ソフトウェア編」ではモニタ程度のものが動いていることが多かったと思いますが、今回はプログラムの実行ができているらしいとわかる程度です。

最も簡単なテストプログラムは実行開始番地で無限ループさせるものでしょう。

HD1-6120(IM6100も)は0FFFH番地から実行を始めますので、ここに0FFFH番地へのJMP命令を置きます。これを実行させておいてアドレスバスの状態を観察するとA0~A11までがすべて"H"になっていて0FFFH番地を読み続けていることがわかります。

次に異なるアドレスでループさせてみます。

HD1-6120でダイレクトにJMPできる先は、同ページ(アドレスの上位5ビットが同じ)か0ページ(アドレスの上位5ビットがすべて0)だけです。それ以外へ飛びたいときは同ページか0ページにアドレスを書いておいて間接アドレッシングを使います。ここでは簡単に0ページで試してみます。

去年入手したHD1-6120、ボード作りかけのまま時間が経ってしまいましたがやっと動くところまでたどり着きました。

いつものようにEMILY Boardを利用します。HD1-6120は12ビットバスなのでEMILY Board +8が必須となります。

基板の表側、搭載部品を見ていきます。

もちろん40ピンの大きなのがご本尊HD1-6120-9です。

以前タイプライタを取り上げましたが、その取説を発見しました。

これが表紙、全部で10ページ程の冊子です。

「スミス・コロナ・スタンダード・ポータブル」というのが名称のようです。一応キャリングケースに入れて持ち運べるので「ポータブル」なのでしょうが、今の感覚ではとても「ポータブル」などと呼べる重さではありません。

本文には「Galaxie Deluxe型とClassic12型のみ」といった記述があり、少なくとも以下のようなバリエーションがあったようです。

うちのは「Classic 12」です。

8080と一緒に買ったキリル文字型番のUV-EPROMです。

2764相当品です。デートコードは「9305」なので1993年でしょうか。

前回予告したようにGAL16V8でオープンドレイン出力を実現するときの制約について書いてみます。

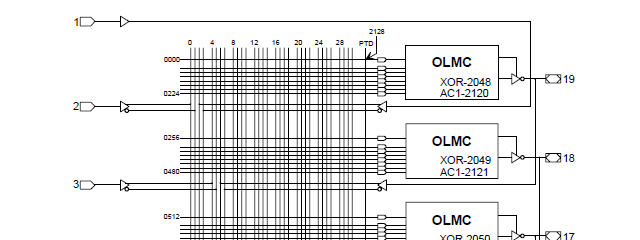

これ説明するためにはGAL16V8の内部構成の知識がある程度必要です。そこでデータシート記載のブロック図を見てみます。

同等の回路が並んでいるのでこれは一部分、全体の約1/3ほどです。

左側の格子状になっている部分がプログラマブルANDアレイ、右側のOLMCと書かれている部分がマクロセルと呼ばれます。

まずはANDアレイからです。

縦の線には各入力ピンからの信号とその反転信号が接続されています。例えば左端の線はピン2の信号、次はその反転信号、その次はピン1の信号といった具合です。動作モードによってはちょっと違う信号もありますが、今のところは気にしなくても大丈夫です。

前回は開発環境を準備したところまで書きました。あとは目的の論理を書くだけと言いたいところですが、ちょっと気になることがあるので先に試してみることにします。

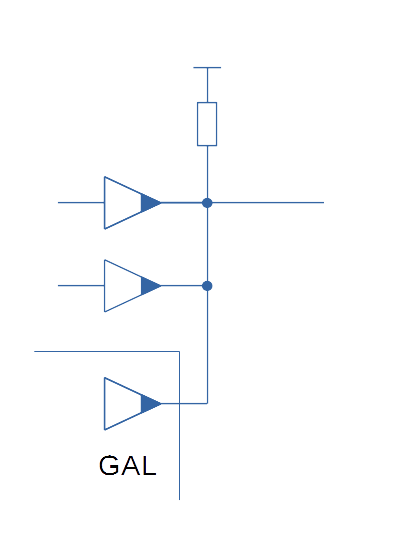

それは以下のような箇所があることです。

オープンドレインによる(負論理の)ワイヤードORです。上の2つは実際は独立したオープンドレインバッファではなくLSIの出力がオープンドレインになっています。

残念ながらGAL16V8にはオープンドレイン出力の機能はありません。探すとオープンドレイン対応のGAL16VP8というものが存在したようなのですが、今さら入手は難しいでしょう。念のためにAliExpressとeBayを見てみましたが発見できませんでした。

ちょっと訳あってGAL動かしてみました。

これまでにも勤め人時代にAltera(今はIntelになっています)のEPM7128とかLatticeのLC5256MVなんかは使ったことがありました。公式には私はソフトウェア担当だったのですが、いろいろあって回路やこのようなPLDの設計も何度かやる機会もあったのです。

個人的にはGALやXilinxのXC9500など必要になったら使えるようにデバイス調達したり書き込み環境準備したりしていたのですが、いつも汎用ロジックで何とかなってしまい実践する機会がありませんでした。

そんな中、機会が到来しました。