第2期工事はFPU MC68881RC16Aの追加です。

基板の空いたエリアにMC68881RC16Aを追加しました。このデバイスはMC68020用の浮動小数点コプロセッサですが、他のプロセッサにもI/Oデバイスとしてなら接続可能です。バス幅も8,16,32どれでも可能でここでは16bitバスで接続しています。クロックもメインのプロセッサは8MHzでこのFPUは16MHzという変なことをしていますが全く問題ありません。

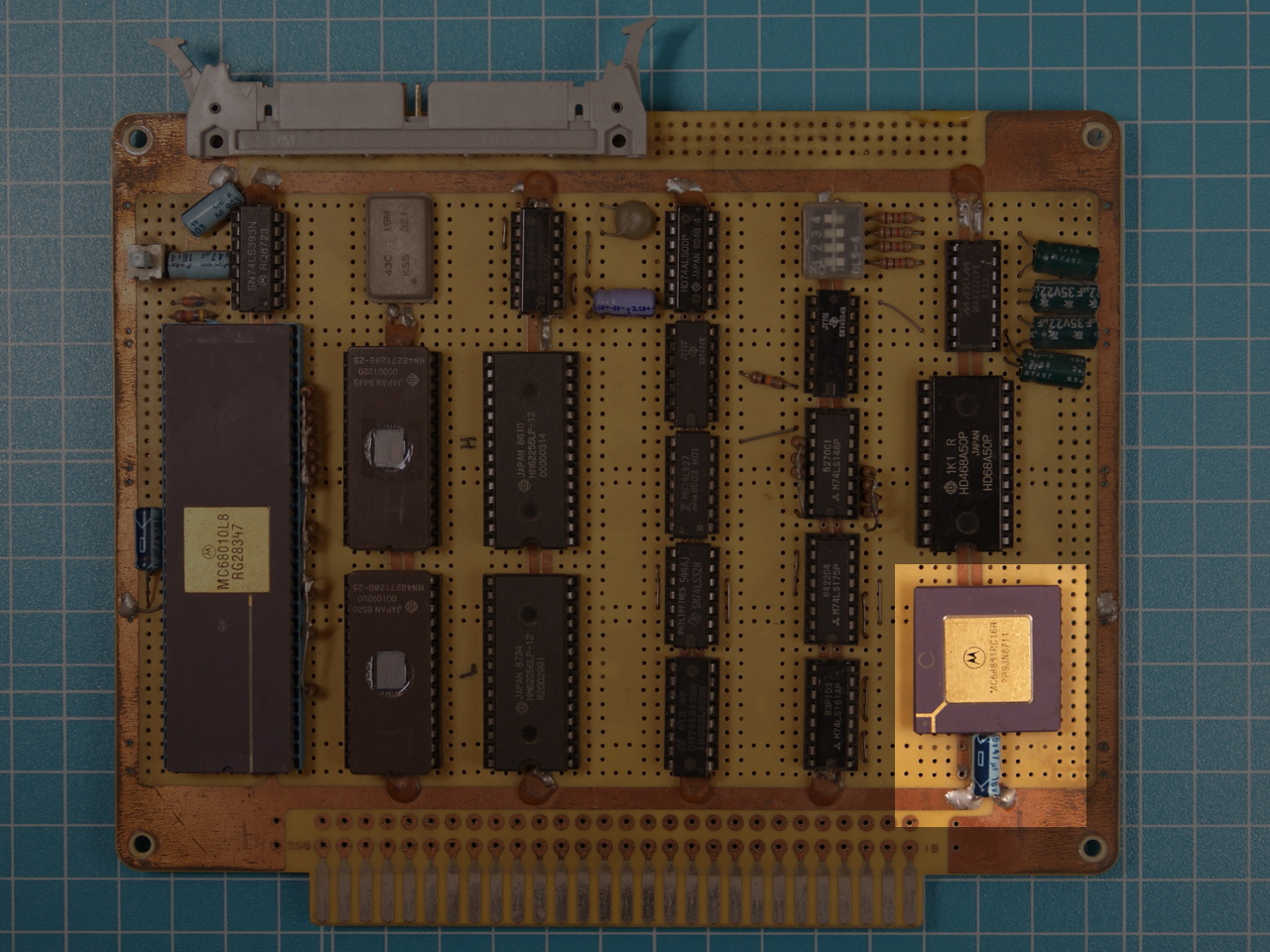

ところで基板写真をよく見るとこの基板はランドがすべて独立した蛇の目基板ではなくDIPを想定したパターンになっています。ここにPGAソケットはそのままでは取り付けられません。そこで大きな四角い穴を開けて裏側から蛇の目基板をあてています。図にするとこんな感じです。

穴はソケットより少し小さく、ソケットのピンの外周より大きくしているので、表から見ると普通に取り付けたように見えます。厳密には背が少し低くなっていますが目立ちませんね。

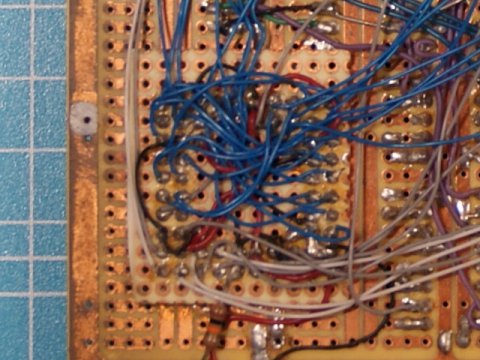

裏から見るとこの部分だけ蛇の目基板が重なっています。

FPUの追加に加え、メインのMPUもEF68000P10からMotorola MC68010L10に替えています。両者はピン互換なので差し替えるだけですが、エラー時のスタックの構造が変わっているのでソフトには若干の変更が必要です。モニタではエラー時にスタックを解析して表示しているのでその部分は変更しました。

なぜ載せ替えたかというと実はあまり意味はありません。MC68010というあまり使われていない珍しいものが手に入ったから(亜土電子で3,500円だったかな)というのが一つ、同クロックでも僅かに速いらしいというのも一つですね。あとはアドレスエラー(奇数番地へ16,32ビットアクセスを行ったときに発生します)を検知して複数の8ビットアクセスに置き換える(ちょっと違った一種の仮想記憶)のを試してみたかったというのもあります。結局これはやりませんでした。

ということでこの時点のスペックは以下のようになりました。

| CPU | MC68010 8MHz | 当初はMC68000 |

|---|---|---|

| FPU | MC68881 16MHz | |

| ROM | 32kB | モニタとTiny BASIC |

| RAM | 64kB | SRAM |

| SIO | 1ch |

Add new comment