カテゴリー

3つ目もまた32ビットRISCマイクロプロセッサです。

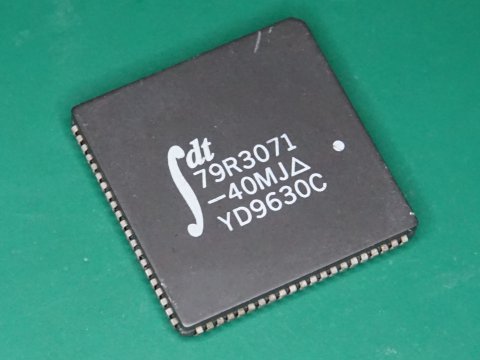

これはIDTの79R3071、いわゆるMIPSプロセッサです。1996年30週の製造かな。

MIPSプロセッサは以前MIPS R4700を取り上げたことがありました。なのになぜこれを買ったのかというとR4700は64ビットバスでありとても手に負えないからです。このR3071なら32ビット(マルチプレクスバスですが)なのでまだ現実的ですし、バイトイネーブルもあります。

MC68020のように下位アドレスとサイズからバイトイネーブルを作るのは意外と面倒で何らかのPLDの使用が避けられません。

i960やAm29000とは違いMIPSは仕事で何度も使ったことがあります。とはいえC言語で書いていただけなのでアセンブリレベルの話は初めてです。

ということでアーキテクチャの特徴をみてみます。

- レジスタ

MIPSの汎用レジスタはサブルーチンコール時に切り替わったりせず常時32個使用できます。r0の値は常に0(代入しても無視される)なこととr31がサブルーチンからの戻りアドレスに使われること以外は平等です。他に乗除算に使用するHI,LOとプログラムカウンタがあります。フラグレジスタに相当するものはありません。

このR3071を含むMIPS Iアーキテクチャではレジスタに値を代入した次の命令でそのレジスタをソースとして参照できないという制限があります。MIPS IIアーキテクチャ以降この制限は撤廃されています。 - 3オペランド

MIPSファミリも演算命令は3オペランドです。 - 遅延分岐

BEQなどの条件分岐やJAL(Jump and Link)などの分岐命令は分岐先の前に直後の命令を実行する遅延分岐です。MIPS II以降には条件を満たさず分岐しない場合には遅延スロットの命令を実行しないタイプが追加されています。 - 条件分岐

レジスタ同士あるいはレジスタと0の比較によって直接条件分岐します。条件付きのサブルーチン呼び出し命令もあります。

分岐以外に条件付き代入命令も存在します。 - 即値

ADDI,ORIなど一部の演算命令では16ビットの即値が使えます。

16ビットを超える即値はまずLUI(Load Upper Immediate)命令で上位16ビットをレジスタにセットします。この命令で下位16ビットは0になります。続いてORI命令で下位16ビットをセットします。ORI命令の代わりにADDI命令でも良さそうに思えますが、ADDI命令は符号拡張される(なのでSUBI命令は存在しません)ので不適です。

下位16ビットのみの即値ロードは出来ないのでORI命令かADDI命令でr0と演算します。両者は符号無しか符号付きかで使い分けます。 - バイト・ハーフワード

基本的にすべて32ビット処理ですが、メモリのLoad/Store時にはサイズを指定した命令があります。Loadの場合はさらに符号拡張かゼロ拡張かで命令が分かれます。

さて、実際に動かすとなると一つ問題が……

愛用しているMacroassembler ASがMIPSアーキテクチャに未対応なんですよね。またコードジェネレータを書くことになるのかな。

参考文献・関連図書

"The IDT79R3071, IDT79R3081 RISController Hardware User's Manual", Revision 2.0, Integrated Device Technology.

Charles Price, "MIPS IV Instruction Set", Revision 3.2, MIPS Technologies.

IDT

IDTって、インテグラルのdtだったのですね。遅まきながらたった今気づきました。よい写真をありがとうございました。

MIPS命令セット

VR4133の暗号ユニットを設計したKO大院卒の後輩の「この(MIPSIII)命令セット考えたやつ、絶対ヘネパタ本読んでない」の発言のインパクトは20年以上経っても忘れない。

Add new comment