今回もPLLというよりVCOの話になっています。

その12で書いたようにVCOのF-V特性が比較的手間がかからず測れるようになったのでいろいろ見てみます。

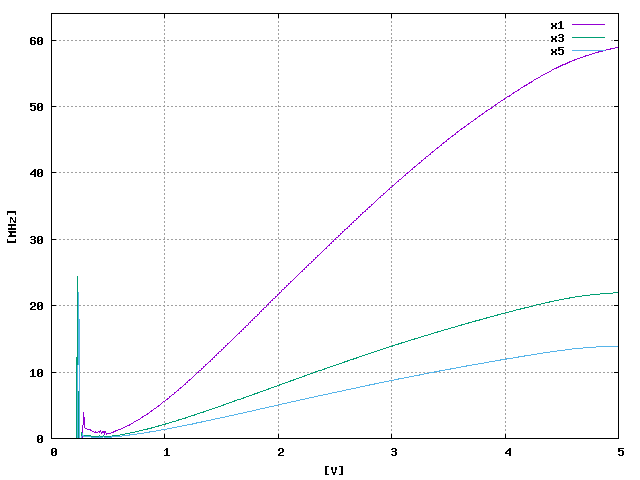

まずはTC74HC14APでリングの段数を1, 3, 5段にしてどうなるかです。

下の方が乱れているのは前回同様ですが、3,5段はかなり酷いですね。

一応私としてはこれが本命と考えています。

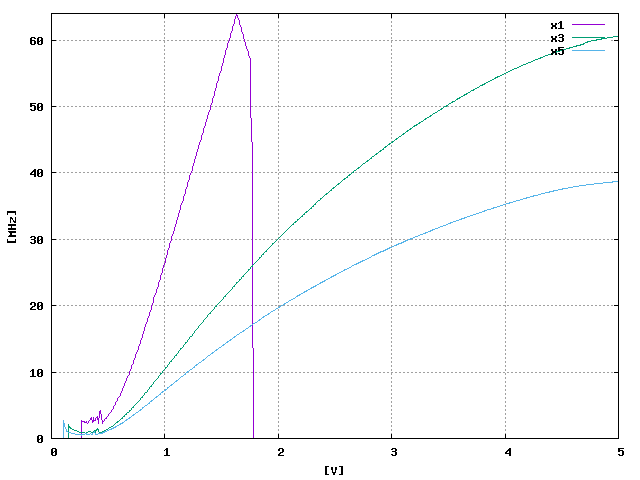

続いてもう少し周波数の高い方の例としてTC74AC04APについて同様に......

1段の場合途中から下がり始めているのはエイリアジングと思われます。ちょうど64MHzで折れていますが、この時AVRに入力されているのは1/16の4MHzです。AVRは8MHzで動作していて、その周波数でサンプリングしているようなのです。

その後ストンと落ちているのはプリスケーラが動作しなくなったのではないかと想像しています。

これ以上の周波数に対応するならプリスケーラの74HC393をより高速な74AC393などに変えて、分周比も1/16から1/64などに変更するといったところですね。あるいは分周比そのままでAVRのクロックを上げるか。

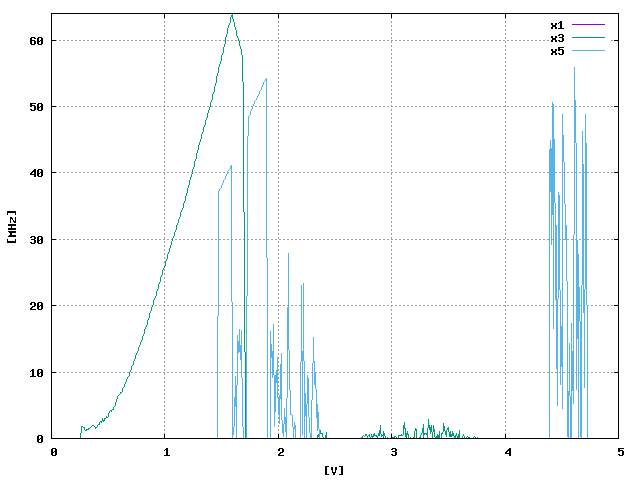

さらに高速のSN74AHCU04も試してみました。

これアンバッファタイプなので1段が発振しないのは予想していましたが、5段もまともに動いていませんね。

こいつはまだ何が起きているか追っていないので詳細不明です。使用予定もないのでそのうち気が向いたら見てみるかな。

他のインバータICもいろいろあるのでそれも気が向いたら測ってみようと思います。かなり手間が減ったとはいえデバイス挿し替えたり段数設定ジャンパ替えたりは手動でやらねばならず、測定自体も時間かかるので意外に面倒なのです。

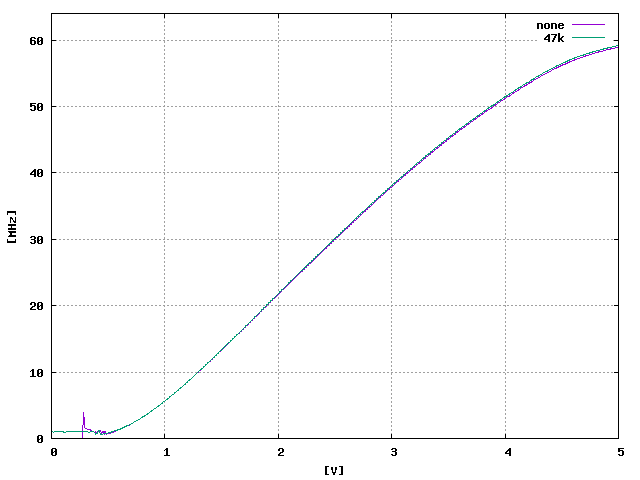

さて、もう一点ちょっと気になることがありまして......

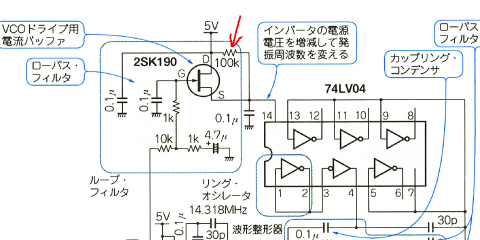

リングオシレータの電源のところはトランジスタ技術1997年6月号の以下の回路を参考にしています。

ローパスフィルタなどは別でFETの部分だけなのですが、赤矢印の100kΩの意味が分かっていませんでした。

そこで付けない場合と47kΩを付けた場合とでVCOの特性を見てみました。

全体的に若干上がっていますが、特徴的なのは下の乱れている部分がほぼフラットになっていることです。これもしかして下の不安定部分を回避するためなのかな。

PLLのVCOはF-V特性が単調でないとそこに引っ掛かってロックできないことがありますからね。

Add new comment