カテゴリー

第4期工事はI/O高速化のためのPIOの追加になります。

第3期工事まででCP/M-68Kが動作するようになりましたが、フロッピーディスクへのアクセスを含め全てのI/Oがシリアルを経由するため遅いという問題がありました。そこでI/O機能を提供しているPC-8001mk2との間により高速な通信路を確保することにしました。

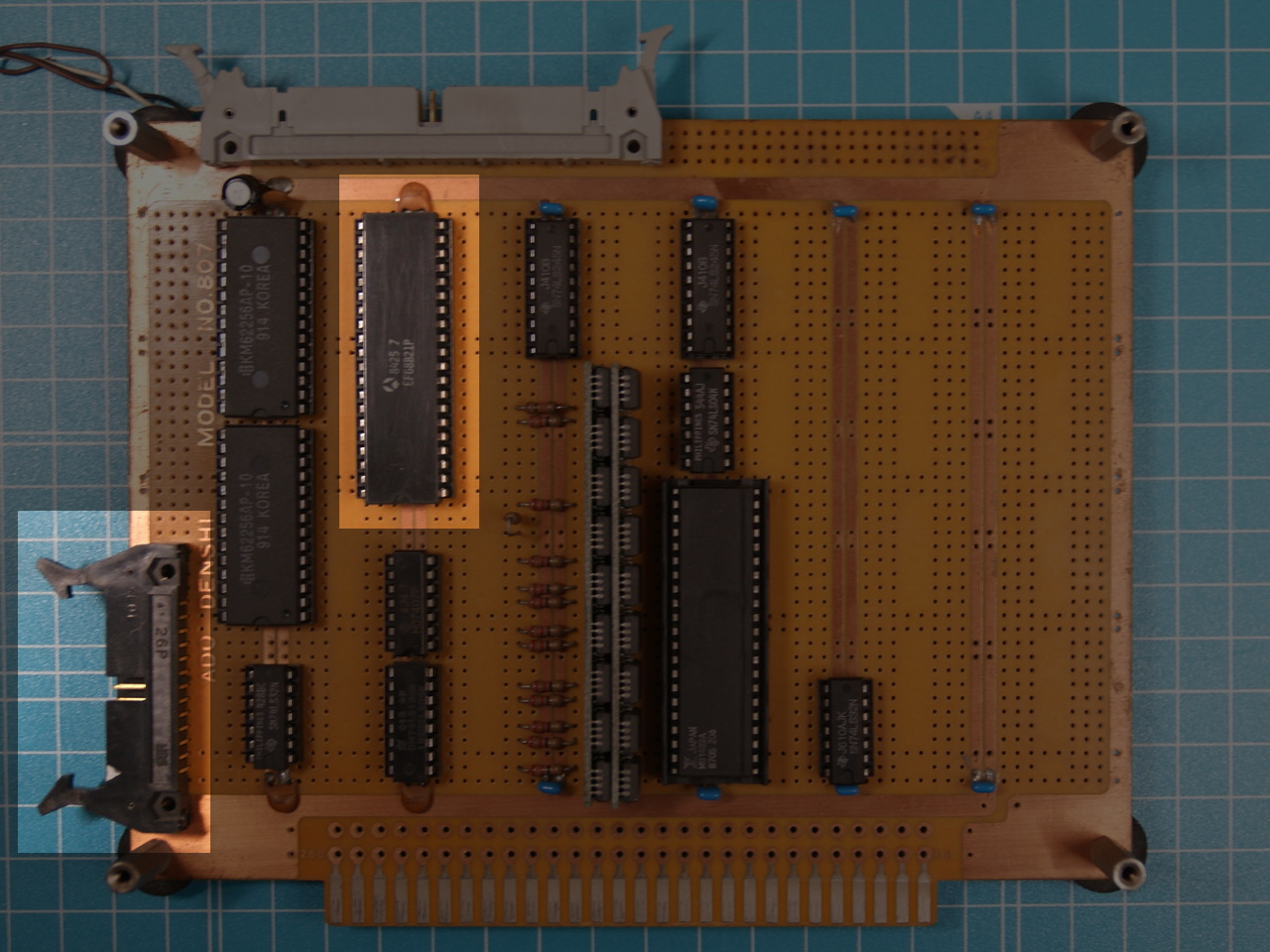

追加したのはEF68B21P PIAです。これはモトローラのMC68B21のトムソン製セカンドソースで、8ビットのポートが2つあるため片方を出力、他方を入力として使用します。

左下の26ピンコネクタを経由し、PC-8001mk2拡張ボード上の8255と接続します。コマンドプロトコル的にはシリアルと全く同一のものを使用しています。

この変更によりシリアルポートは他の用途に使用できることになりました。これはCP/M的にはRDR(Tape Reader)・PUN(Tape Puncher)のデバイスとして扱うことが可能ですが、そのためのBIOS変更を行ったのか記憶がはっきりしません。特に接続したいものがあったわけではないので、そのままになっていたかもしれません。

この時点での仕様は以下の通りです。

| CPU | MC68010 8MHz | 当初はMC68000 |

|---|---|---|

| FPU | MC68881 16MHz | |

| ROM | 32kB | CP/M-68k起動用 CP/M移植まではモニタとTiny BASIC |

| RAM | 128kB | SRAM |

| PIO | 8bit ×2 + ハンドシェイク | パラレルといってもプリンタポートではなく、パソコンのI/Oを借りるための専用I/O |

| SIO | 1ch |

関連項目

Add new comment