カテゴリー

先日のNS32C201とともに入手したデバイスです。というよりこちらがメインでNS32C201がついでだったのですが。

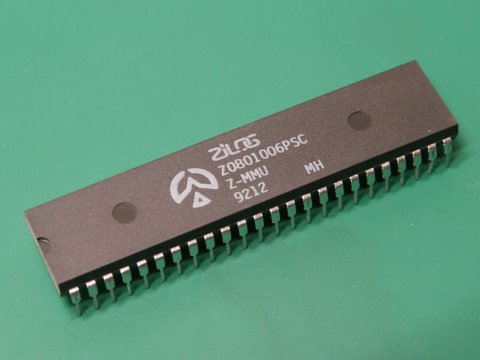

これはZ0801006PSC、Z8001用のMMUです。

これは6MHz品ですが、他に4MHz,8MHzのものが存在するようです。持っているZ8001 CPUが6MHz品なのでMMUだけ8MHzでも意味がありませんのでこれで十分です。

これは1992年製、「MH」は何の意味でしょう? 工場か製造国の記号なのではないかと想像していますが確かなことはわかりません。

論理アドレスと物理アドレスのピンが必要なことから48ピンという比較的大きなパッケージに入っています。これでも論理アドレスとMMUのレジスタアクセス用のデータバスがマルチプレクスされているので、もしそうでなかったらさらに8ピン増えていたところです。

ちなみにNS32016用のMMU NS32082では論理アドレスと物理アドレスもマルチプレクスされています。MMUはCPUからのHLDA(ALEにあたる信号)で論理アドレスをラッチし、変換後にHLDAOを出力して外部で物理アドレスをラッチする仕掛けです。どうせ変換に1クロックかかるならこれによる時間のロスは無いというわけです。ピン数はそれでも48ピンなのですが。

論理アドレスと物理アドレスがマルチプレクスされているのはMMUをオプションにしてソケットのみ実装するシステムではありがたいでしょう。アドレスをバイパスさせる必要がなく、ラッチ信号を細工するだけで済ませられますから。

論理アドレスと物理アドレスがマルチプレクスされているのはMMUをオプションにしてソケットのみ実装するシステムではありがたいでしょう。アドレスをバイパスさせる必要がなく、ラッチ信号を細工するだけで済ませられますから。

話をZ8010に戻すと、AD0~AD7は接続されていないので注意が必要です。アドレス変換に下位アドレスは不要であり、MMUレジスタの変更のためだけにピンを増やすことも無いという判断なのでしょう。

ここで外付け(プロセッサ内蔵ではない)MMUをいくつか挙げてみましょう。

| 型番 | 名称 | パッケージ | プロセッサ | 物理アドレス | 備考 |

|---|---|---|---|---|---|

| ZEN1011P | DIP40 | Z80 CPU | 1MB | 『プロセッサ』1987年2月号に解説記事あり | |

| MC6829 | MMU | DIP40 | MC6809 | 2MB | |

| MC68451 | MMU | DIP64 | MC68000 / MC68010 | 1つで32のセグメントを管理、必要に応じて複数使用可 | |

| MC68461 | SMMU | PGA | MC68020 | ||

| MC68851 | PMMU | PGA181 ? | MC68020 | 4GB | |

| Z8010 | Z-MMU | DIP48 | Z8001 / Z8003 | 16MB | |

| NS32082 | MMU | DIP48 | NS32016 / NS32032 / NS32332 | 32MB | |

| NS32382 | MMU | PGA152 | NS32332 | 4GB | |

| MC88200 | CMMU | PGA | MC88100 | 4GB | キャッシュコントローラ機能を含む キャッシュ容量を16kB⇒64kBにしたMC88204もある |

Z8030 SCCも一緒に手に入れたのですが、それはまた後日書きたいと思います。

参考文献・関連図書

Z8010データシート, Zilog.

松村繁(1987)「Z80用MMU ZEN1011Pを使用したワンボード・コンピュータの製作」,『プロセッサ』1987年2月号,pp.59-85,技術評論社

Add new comment